Pakistan’s technological advancement hinges on robust digital infrastructure. The impending arrival of PCIe 8.0 bandwidth marks a significant structural upgrade, poised to redefine data transfer speeds in modern computing. PCI-SIG has strategically unveiled PCIe 8.0, a formidable interconnect standard designed to deliver an unprecedented 1 TB/s of bidirectional bandwidth in a x16 configuration. This development is a direct response to the escalating data demands from artificial intelligence, high-performance computing, and advanced networking, promising a crucial catalyst for system efficiency and maintaining backward compatibility with prior generations.

The Translation: Deconstructing 1 TB/s PCIe Bandwidth

Understanding the implications of PCIe 8.0 requires clarifying its core metrics. The standard targets 256.0 GT/s (Gigatransfers per second) per lane. This signifies the raw data transfer rate, distinct from gigabits per second, as it includes overhead. Consequently, a x16 configuration, which utilizes 16 lanes, can achieve the advertised 1 TB/s (Terabyte per second) of bidirectional bandwidth. This structural leap transcends prior limitations, ensuring data movement keeps pace with processor advancements, a critical factor for achieving optimal system performance.

Historically, system performance was predominantly constrained by processing power. However, with the advent of data-intensive workloads, efficient data movement has emerged as the bottleneck. PCIe technology, therefore, evolves beyond simple CPU-to-endpoint connectivity, structurally enabling lower latency, improving scale-out performance, and supporting GPU compute scaling across multiple CPUs. Furthermore, the strategic deployment of PCIe switches and retimers, alongside advancements in copper and optical connectivity, robustly extends PCIe’s operational reach beyond conventional system boundaries.

Socio-Economic Impact: Empowering Pakistan’s Digital Citizens

The operationalization of PCIe 8.0 bandwidth will fundamentally alter the daily digital experience for Pakistani citizens. For students, this translates to significantly faster downloads of large datasets for research or multimedia projects, enhancing academic efficiency. Professionals in fields like engineering and design will experience accelerated data processing for complex simulations, leading to calibrated project timelines. Households, especially those with multiple users engaged in high-bandwidth activities like 4K streaming or online gaming, will benefit from reduced latency and seamless connectivity.

This technological leap supports a more resilient digital economy. Businesses, particularly those leveraging cloud infrastructure or AI-driven analytics, will achieve higher operational throughput. For instance, data centers can process information at an unprecedented pace, providing more responsive services. Consequently, this enhances Pakistan’s overall digital literacy and capacity, positioning the nation for advanced technological integration and innovation across various sectors.

The Forward Path: A Momentum Shift for National Advancement

This development represents a definitive “Momentum Shift” for Pakistan’s digital landscape. The doubling of bandwidth, maintaining existing software models and platform architectures, provides a robust pathway for seamless integration. This strategic foresight ensures that as computing demands escalate, our foundational infrastructure remains ahead of the curve, providing a baseline for future innovation. It is a structural advancement that not only addresses current challenges but also proactively positions Pakistan to harness emerging technologies with precision and efficiency.

Calibrating for Future Data Demands: The PCIe 8.0 Bandwidth Imperative

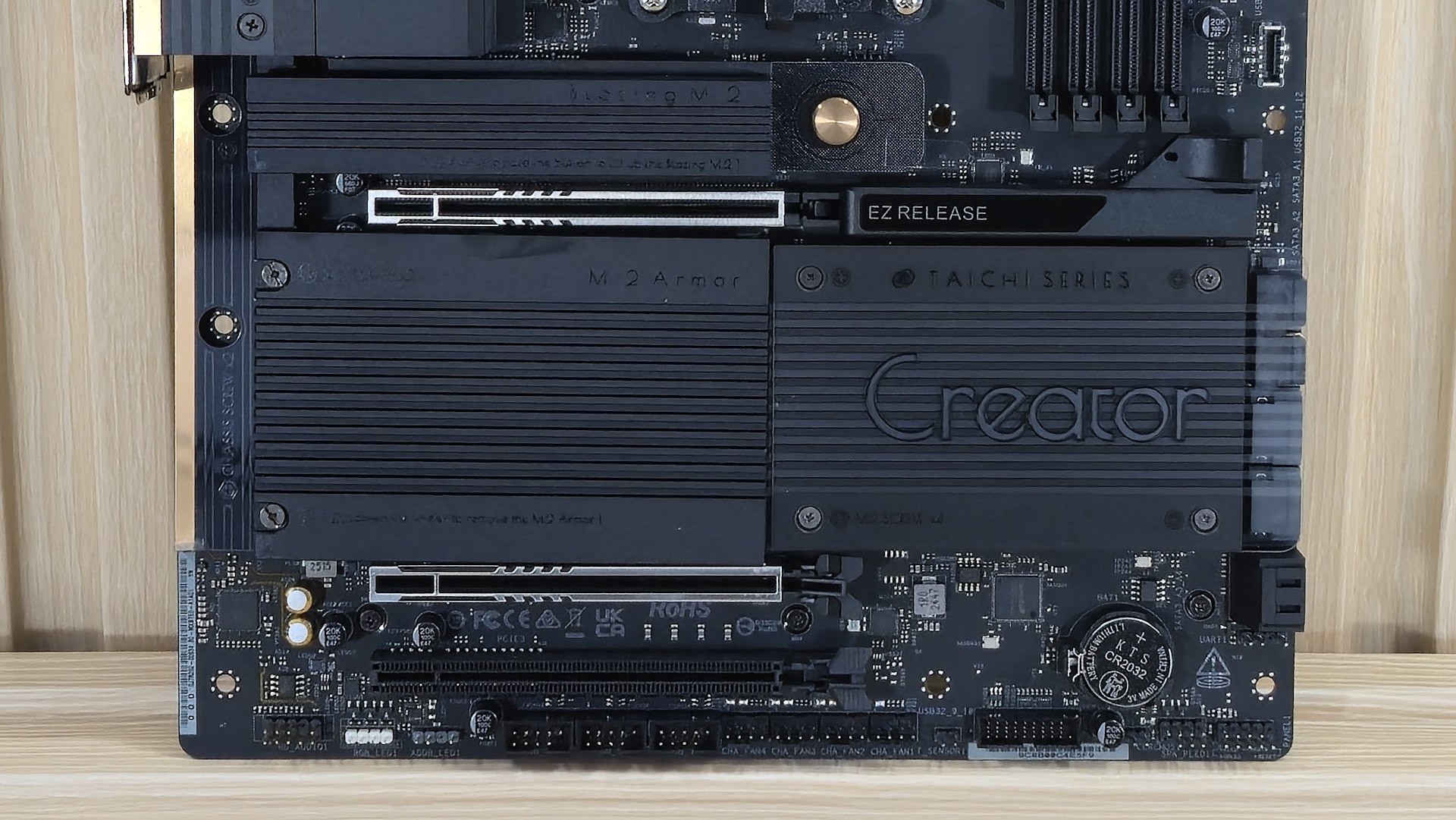

PCIe 8.0 systematically continues the industry trend of doubling bandwidth approximately every three years. This calibrated approach enables system designers to scale performance without requiring wholesale changes to existing software models or platform architectures. At the system level, the new standard is strategically engineered to improve CPU-to-accelerator communication, enhance accelerator-to-accelerator scaling, and increase the utilization of memory and networking resources. For designers of system-on-chip (SoC) and accelerator platforms, the focus intensifies on achieving efficient data handling at these higher speeds while meticulously maintaining protocol efficiency and scalability.

Precision Engineering: Navigating New Technical Hurdles

Operating at 256 GT/s introduces distinct engineering challenges for system design. Reliable performance at these unprecedented speeds necessitates close coordination between controllers and physical layer components. Key areas requiring meticulous attention include link training, signal equalization, and robust error management across diverse system configurations. Leading companies, such as Rambus, are actively working on controller and PHY integration, alongside ensuring comprehensive interoperability across switches and retimers. Furthermore, the industry proactively explores extending PCIe connectivity beyond traditional printed circuit boards, with advancements in copper cabling supporting connections over several feet and ongoing optical PCIe research targeting reach up to several meters.

Baseline for Stability: Validation and System Integration

As data transfer speeds logarithmically increase, the process of validation becomes an even more critical component of system development. Successful PCIe 8.0 deployment is precisely dependent on accurate modeling, rigorous system-level testing, and guaranteed interoperability across the entire ecosystem. Controller technologies, therefore, play a central, structural role in managing link setup, sophisticated error handling, and overall system stability. Early strategic planning and alignment with system requirements will prove essential for companies developing next-generation SoCs and accelerator platforms to harness the full potential of this advanced standard.